5分钟阅读 -ASML,2022年2月16日

超过55年的摩尔定律一直是半导体行业进步的指导原则。正如最近的发展和行业路线图所示,摩尔的法律将继续进行,即使开发的发展正在发生变化。

1965年,戈登·摩尔(Gordon Moore)是当时的Fairchild半导体研发主任,后来将继续找到芯片制造商英特尔(Intel) - 撰写了一本关于未来的杂志社论半导体芯片在未来十年。该文章包括有关筹码生产的技术能力和经济学的简单观察。

“最低组件成本的复杂性每年大约增加了两倍。当然,在短期内,如果不增加,则可以持续。从长远来看,增加的速度是更不确定的是,尽管没有理由相信它至少要在10年内不会保持恒定。这意味着到1975年,最低成本的每个集成电路组件数量将为65,000。”

将更多组件塞入集成电路上,电子,第38卷,第8号,1965年4月19日

该声明的预测部分仅仅是当前进度率的延续。摩尔本人后来将其描述为“狂野的外推”。但是,这种推断成真,行业中的人们开始进一步向前扩展它。

随着时间的流逝,这一观察被视为半导体行业进步的指导原则:摩尔定律。但实际上,从科学意义上讲,这绝不是实际的“法律”。尽管它确实描述了该行业的令人印象深刻的成就,但其预测能力更像是(高度雄心勃勃的)目标或路线图,该目标是半导体行业所施加的。与任何物理原则相比,它的采用程度更多的是经济学的驱动力 - 以实惠的价格保持微芯片功能的前进。

不断发展的常数

当我们谈论摩尔的法律生存了50多年的同时,它在那段时间经常演变。摩尔对最低成本成本的复杂性的最初观察已转化为各种等效陈述,现在法律通常以芯片加倍的晶体管数量的速度表示。

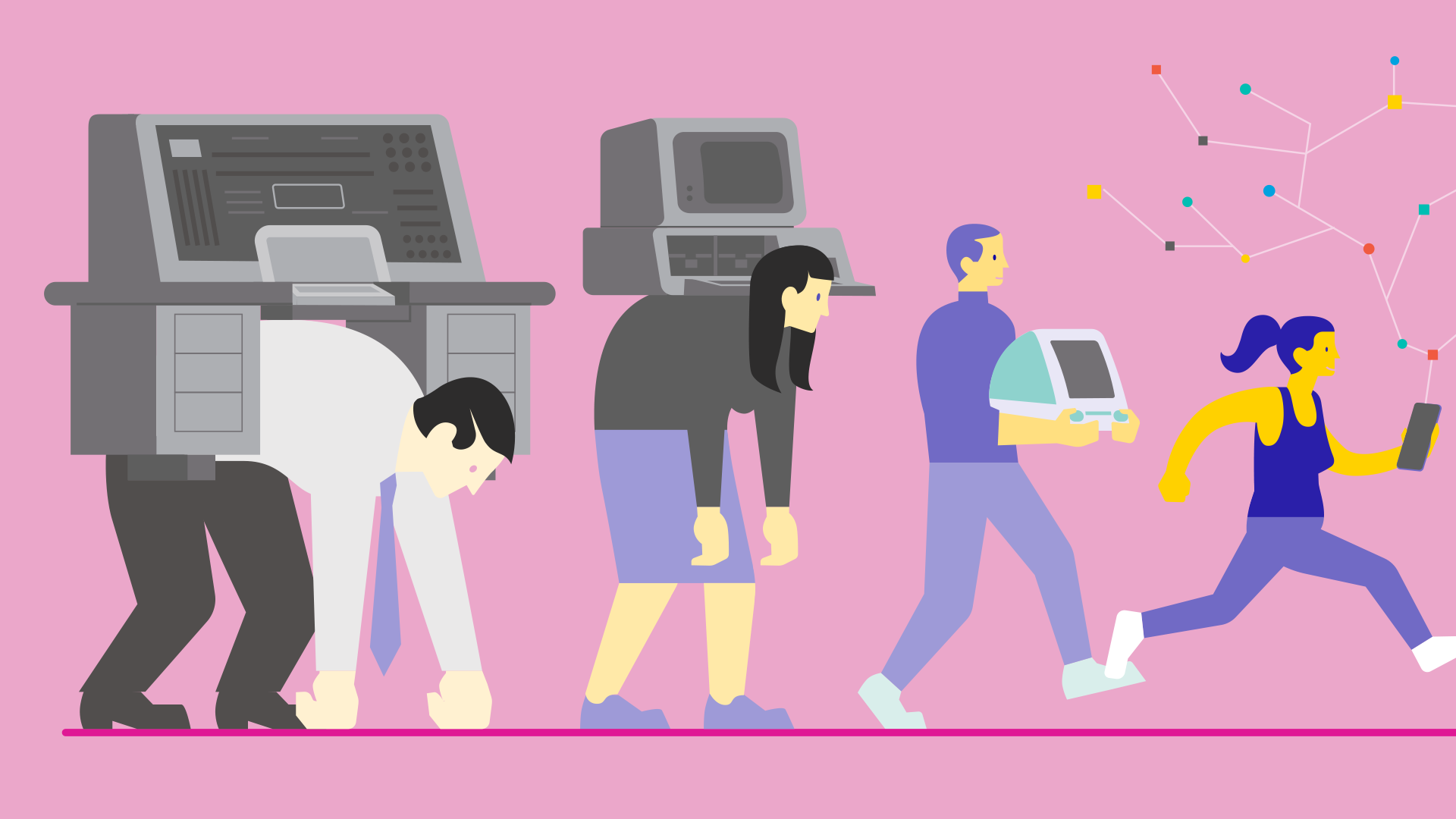

Aad Goudappel的插图。

这种加倍的速度也根据行业和技术的进步而改变(摩尔本人在1975年预测):从最初的一年到两年,这仍然是行业的步伐。万博manbetx官网登录但是,尽管细节的细节已经改变,但摩尔定律的本质仍然是以令人叹为观止的速度发展的路线图。

那种不断收缩的感觉

最初,晶体管计数的这种进度和加倍是通过摩尔描述的三个因素来传递的,因为降低了尺寸,尺寸降低(通常称为尺寸缩放或收缩)以及设备和电路聪明。

维度缩放大部分是由光刻过程和技术。在过去的几十年中,这包括迁移到紫外光的较短波长和镜头的开口角(NA)的开头,以及引入浸入式光刻,多个图案策略以及最近的EUV石印象的引入。

由于光刻启用了较小的功能,因此芯片制造商可以将更多的晶体管打包到同一区域,从而使芯片的功能增加,同时使成本负担得起。结果,尺寸缩放使半导体行业与摩尔定律保持同步超过四十年。

道路的尽头?

较小的晶体管运行速度更快,需要更少的功率。结果,摩尔定律已成为提高芯片性能和能源效率的持续动力的代名词。但是,在某个时候,小尺寸开始干扰晶体管的操作,打破了大小与性能之间的关系以及能源效率。

对于迄今为止大多数微芯片中使用的晶体管的类型,该行业在2000年代中期附近的突破点接近。晶体管在相同的速度下仍然越来越小,但是芯片性能的改善速度较慢。

多年来,微芯片设计和生产发生了巨大变化。

前进的新道路

但是,正如摩尔在1975年所反映的那样,制作较小的功能只是提高芯片性能的一种方法。几十年来,半导体行业还通过设备和电路聪明(用于制造晶体管的材料和结构的创新)提高了芯片性能。这种方法称为设备缩放。例如,使用诸如“低K介电”之类的材料可改善晶体管的电性能。

从根本上讲,不断开发新的晶体管体系结构,以克服传统晶体管的尺寸限制。为此,该行业已经基于所谓的FinFets推出了芯片,这些芯片在类似于鳍的硅表面上使用薄但相对较高的结构。FinFets是一种称为3D晶体管的新型晶体管中的第一个。

尺寸和设备缩放涉及晶体管本身的进化。近年来,通过在系统级别的创新来实现绩效提高,从而可以使用现有的晶体管技术进行进一步扩展。

实现这一目标的一种方法是通过更大的片上集成,例如将处理器,内存和辅助功能组合到一个芯片中,并且3D NAND FLASH,在彼此顶部生产多层闪存以增加同一区域的存储容量。另一个选择是使用新颖的包装解决方案将多个优化的芯片集成到完整的系统中,通常是通过将芯片彼此堆叠来。

接下来的十年

在过去的15年中,这些方法共同使摩尔的定律保持健康。并查看整个行业的路线图,有充分的证据表明他们将在未来十年及以后维持它。

当然,在设备方面,有足够的计划创新可以继续进行缩放路线图,至少有1 nm的节点,其中包括闸门的FET,纳米片FET,FORKSHEET FET和互补的FET。这些发展将通过光刻分辨率的改进(预计每六年左右缩小两倍)驱动的进一步的维度缩放来补充,并且通过边缘放置误差(EPE)来衡量的准确性。

ASML的持续创新动力将支持这一趋势。我们的EPE路线图,这是我们整体光刻作品集的关键,将通过进一步改进我们的应用程序中的光刻平台和发展(包括)计量和检查)路线图。EUV光刻,ASM万博manbetx官网登录L独有的技术现在正在大量生产中,可以在5 nm节点上更简单,具有成本效益的生产。我们目前还在下一代光刻平台-High-Na(EUV 0.55 NA)上工作,这将允许在1 nm节点左右的单个暴露生产。

此外,我们可以期望系统级的扩展比迄今为止的角色要大得多。在过去的一年中,记忆制造商生产了3D NAND芯片,彼此之间具有176个记忆层,并在2030年左右宣布了600多个记忆层的芯片路线图。除此之外,创新的形状还鲜为人知。但是,如果摩尔定律的55年历史向我们展示了一切,那就是半导体行业充满了新发展的想法。只要我们仍然有想法,摩尔的定律就会保持活力并踢。

想深入研究吗?