## Litho today, litho tomorrow

#### Martin van den Brink President & Chief Technology Officer

31 October 2016

## Overview

### **ASML**

Public Slide 2 October 31, 2016

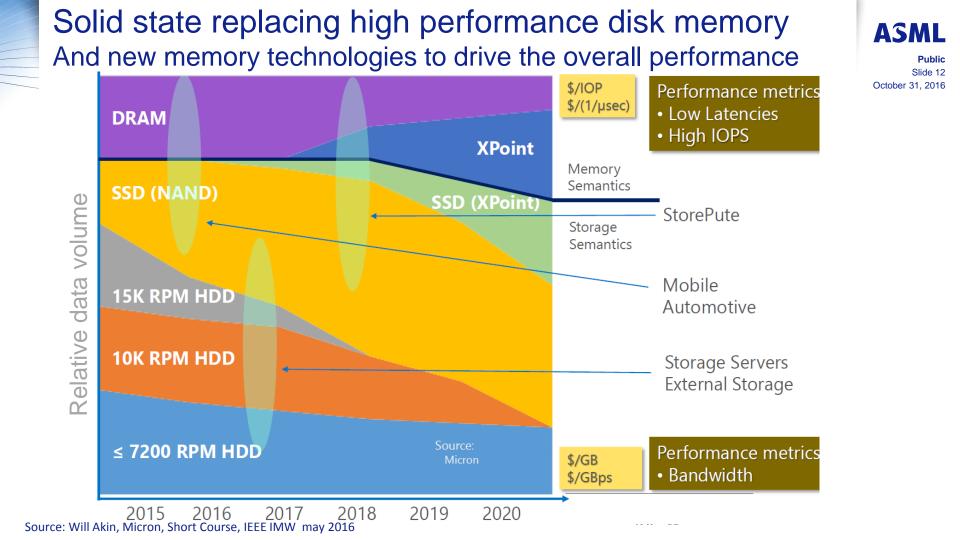

| Industry trends         | <ul> <li>Application trends and economics in our ecosystem are driving increasing<br/>demand for processing power, high-speed memory, and low-cost storage,<br/>fueling the continuation of Moore's law</li> </ul> |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Semiconductor<br>impact | <ul> <li>Continuation of Moore's law will be supported by improving patterning solutions,<br/>achieving fast yield ramp-up, to realize attractive economics</li> </ul>                                             |

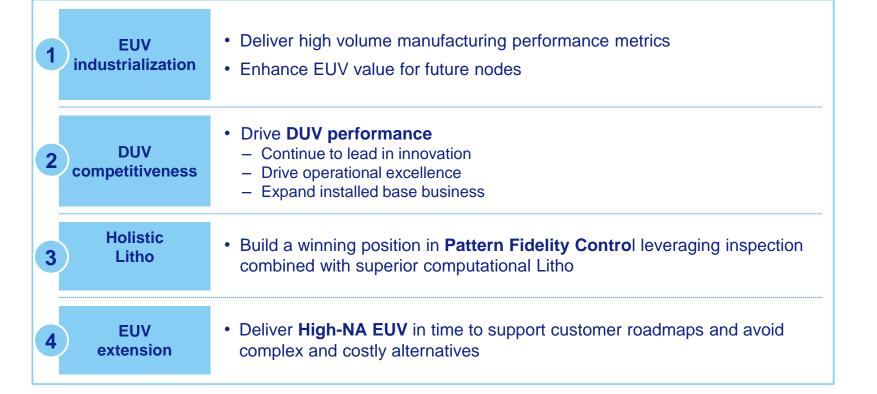

| Strategic<br>priorities | <ul> <li>As a result, our strategic priorities are: EUV industrialization, DUV<br/>competitiveness, leadership in Holistic lithography and EUV extension with High<br/>NA</li> </ul>                               |

| Lithography<br>Roadmap  | We have underpinned our priorities with a detailed product roadmap                                                                                                                                                 |

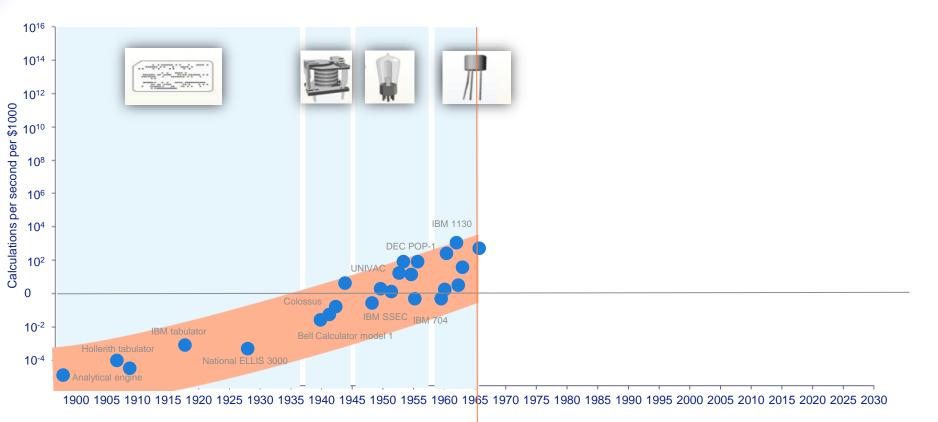

#### The world before 1965 was already on a Moore's like law **ASML** ... computing speed/€ had been doubling every 2 years for 65 years Public

Slide 3 October 31, 2016

Source: Ray Kurzweil

Moore's Law

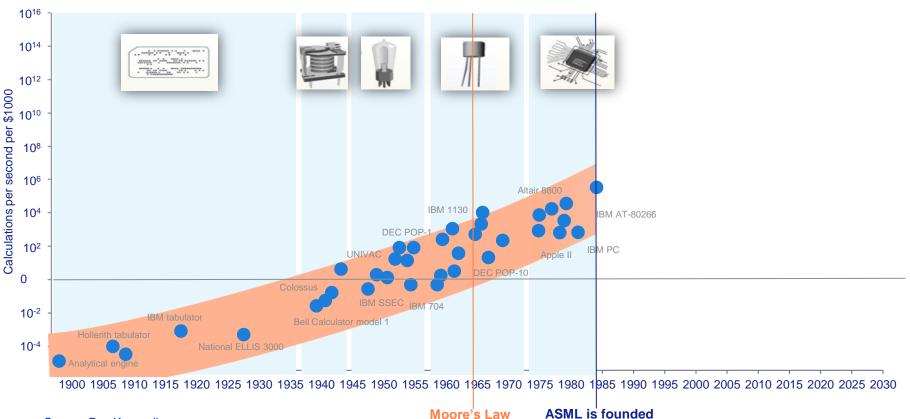

## When ASML started Moore's law was effective for 84 yrs **ASML**

Public Slide 4 October 31, 2016

Source: Ray Kurzweil

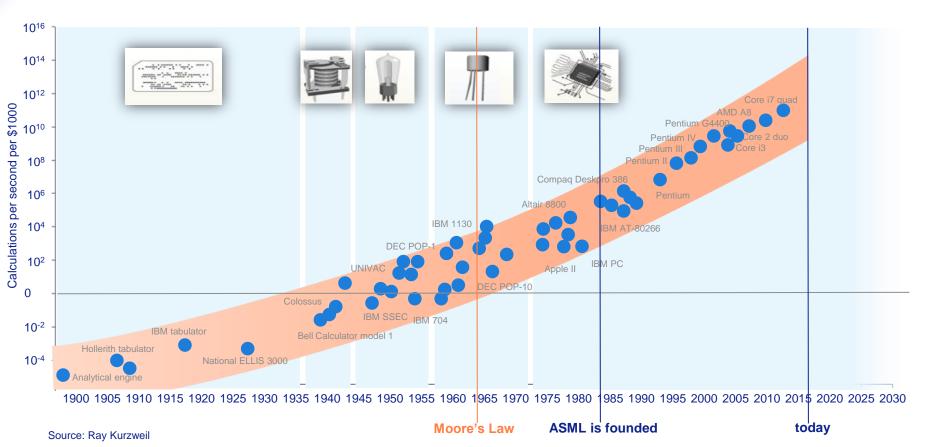

## Today Moore's law is effective for 116 years

Public Slide 5 October 31, 2016

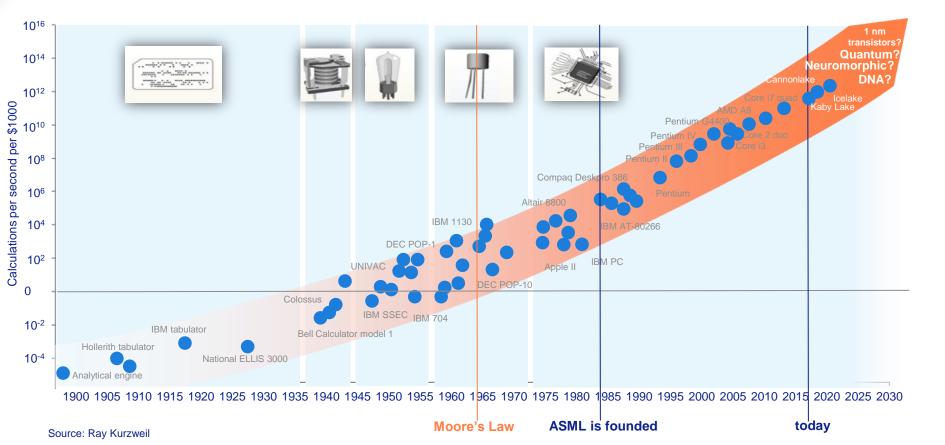

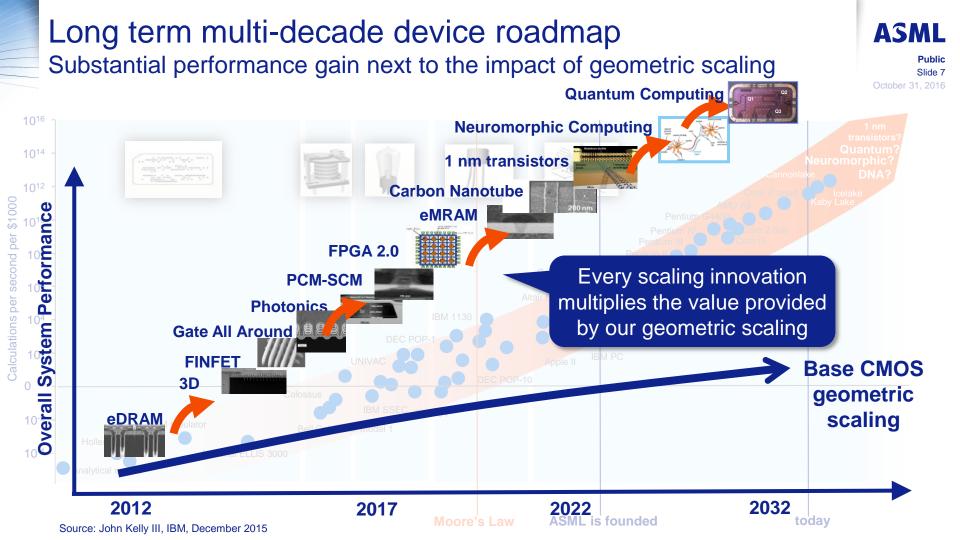

## Can exponential curves continue forever? Moore's Law is likely not slowing down as long as new idea's

Public Slide 6 October 31, 2016

# Application trends in our industry drive continued demand for Moore's Law

### **ASML**

Public Slide 8 October 31, 2016

#### Industry trends towards 2020 and beyond

50B connected **Internet of Things** devices – needing low-cost devices and generating large data volumes requiring storage and processing

89 million **connected cars** on the road of which 6 million **self-driving** – generating and processing >1 GB of data per second each

250 million **personal health** wearables and connected pharmaceuticals for health data collection

Explosion of **(mostly unstructured) data**, growing to >40 Zetabytes from 5 Zetabytes today ...drive a reinforcing cycle of data creation, transmission, storage and processing...

Very high volumes of lowcost semicon devices

Massive computing power and performance memory in-cloud and in-vehicle

semi prod mem logic

Ultrafast & high-band-width network infrastructure ...driving demand for both low-cost and high performance semiconductor products in both memory and logic

...enabled by the continuation of Moore's law...

...which underpinned by an ecosystem with combined profits of >290B\$

Source: McKinsey, ASML

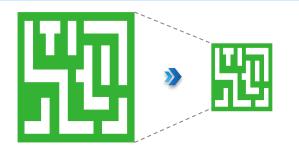

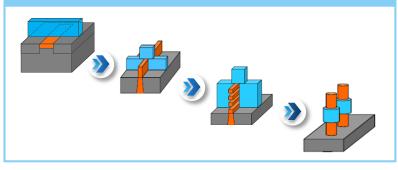

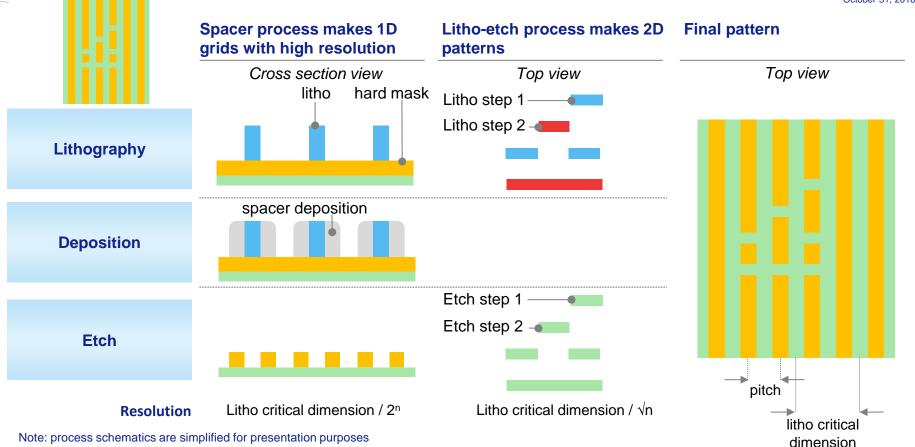

## Geometrical scaling critical in support of Moore's law now enabled trough 4 engines of innovations

**Geometric scaling** 2D shrink through patterning

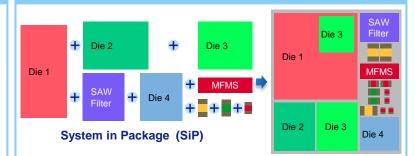

**Circuit scaling** System-on-chip and advanced packaging

**Device scaling** New devices and materials

#### Architecture scaling Solution optimization

Public Slide 9 October 31, 2016

ASML

Source: IMEC, customers

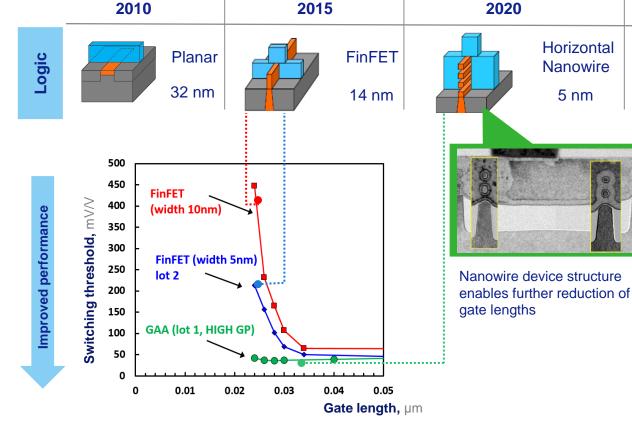

## Logic device and shrink roadmap New devices for 5 nm and beyond are demonstrated to work

Slide 10

2025 >2025 Vertical Nanowire ~2.5 nm ~ 1 nm

One nanometer transistor, UC Berkeley

Carbon nanotul

Zirconium

dioxide

- High-K

- III-V

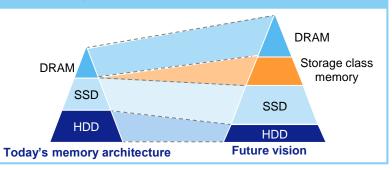

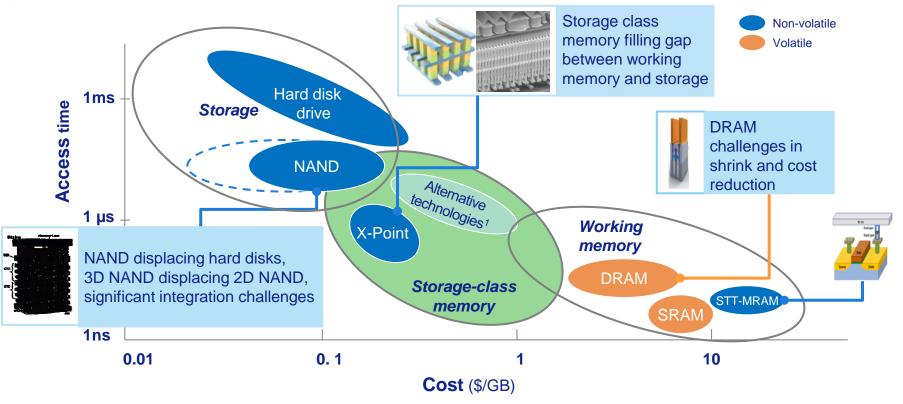

# Large innovation ongoing in memory, driving continued litho demand

Public Slide 11 October 31, 2016

1 Alternative technologies (e.g., CBRAM, PCRAM) likely high litho volume and performance

Source: Western Digital

## EUV could simplify customers' patterning process

Public Slide 13 October 31, 2016

ASML

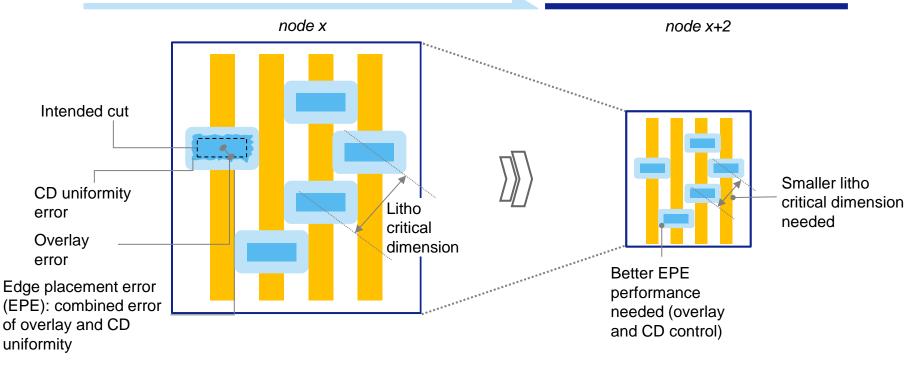

## Edge placement error & litho critical dimension challenges ASML are main factors for continued shrink

Slide 14 October 31, 2016

Edge placement error (EPE) and litho critical dimension (CD) main patterning parameters...

...and shrink requires ever tighter requirements

## Single Exposure lithography is most attractive

optimizing cost, cycle time, yield and edge placement challenges

Slide 15 October 31, 2016

## Industry Shrink Roadmap & EUV insertion

Public Slide 16 October 31, 2016

**EUV Production**

Source: 1) Customers - public statements, IC Knowledge LLC; 2) ASML extrapolations

## Strategic priorities to meet customer requirements Grow our Litho business by delivering superior customer value

**ASML**

Public Slide 17 October 31, 2016

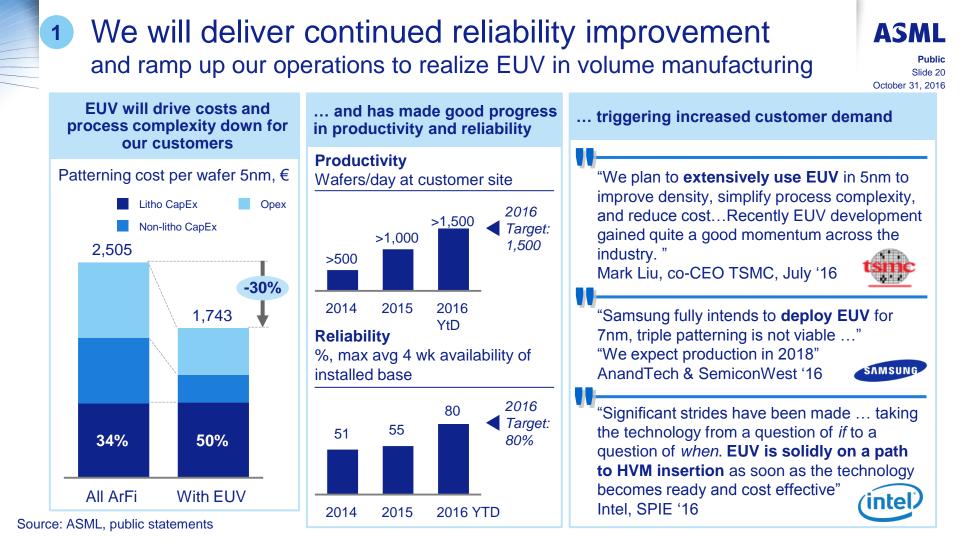

#### 1 EUV key to drive cost effective device shrink roadmaps ASML and simplifying immersion multiple patterning University of Stide 18 October 31, 2016

|                       | Node         | D20-22          | D1X             | D1Y                | D1Z                |

|-----------------------|--------------|-----------------|-----------------|--------------------|--------------------|

| <b>DRAM</b><br>Active | ArFi 1.35 NA | SE              | LE <sup>2</sup> | PD+LE <sup>2</sup> | PQ+LE <sup>2</sup> |

| Cut                   | EUV 0.33 NA  |                 |                 | SE                 | SE                 |

|                       |              |                 |                 |                    |                    |

|                       | Node         | 16-14nm         | 10nm            | 7nm                | 5nm                |

| Logic<br>Cuts &       | ArFi 1.35 NA | LE <sup>2</sup> | LE <sup>3</sup> | LE <sup>3~4</sup>  | LE <sup>6~8</sup>  |

| Vias                  | EUV 0.33 NA  |                 |                 | SE                 | SE                 |

|                       |              |                 |                 |                    |                    |

Plan

Possible but challenging

SE = Single Exposure,  $LE^n$  = Litho-Etch, n # repeats, PD = Pitch Doubling, PQ = Pitch Quadrupling

PoR, Process of Record

Source: Britt Turkot, Intel, 2016 international symposium on EUV, 24 October 2016, Hiroshima Source: TSMC, Semicon Taiwan, Sep 2016

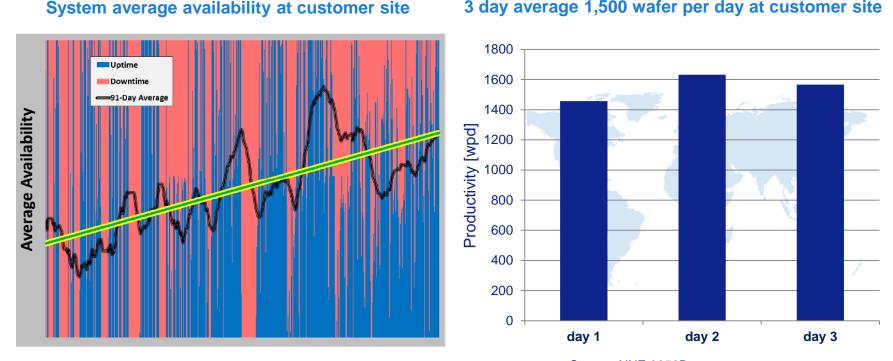

3 day average 1,500 wafer per day at customer site

#### EUV industrialization: productivity and consistency 1 >1500 wafers per day at customer fab, variability needs improvement

Slide 19 October 31, 2016

Public

Source: NXE:3350B

· Each bar represents customer wafers exposed on one individual dav

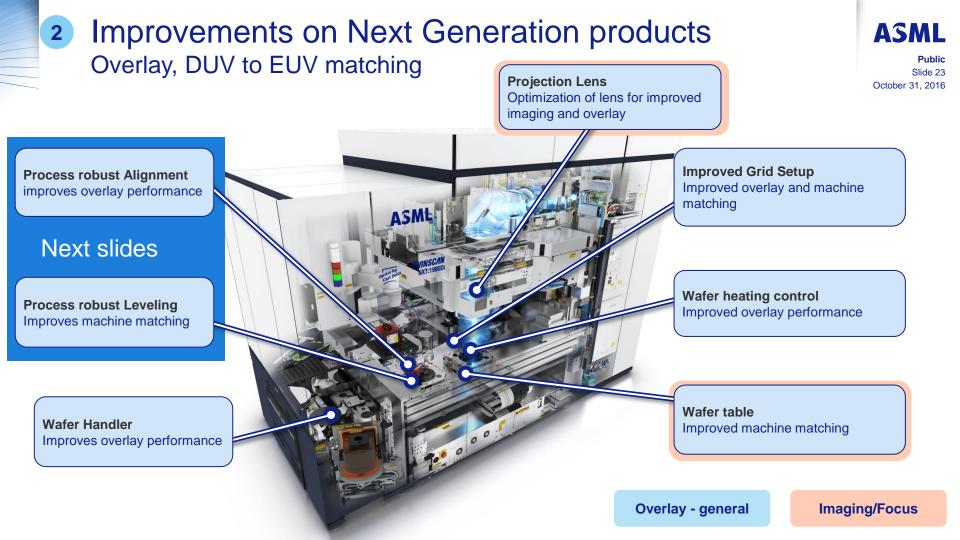

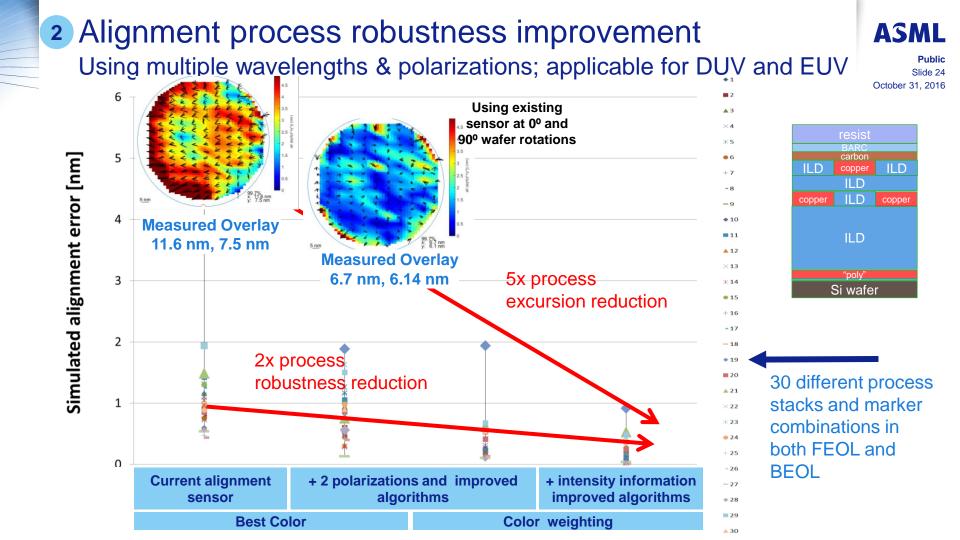

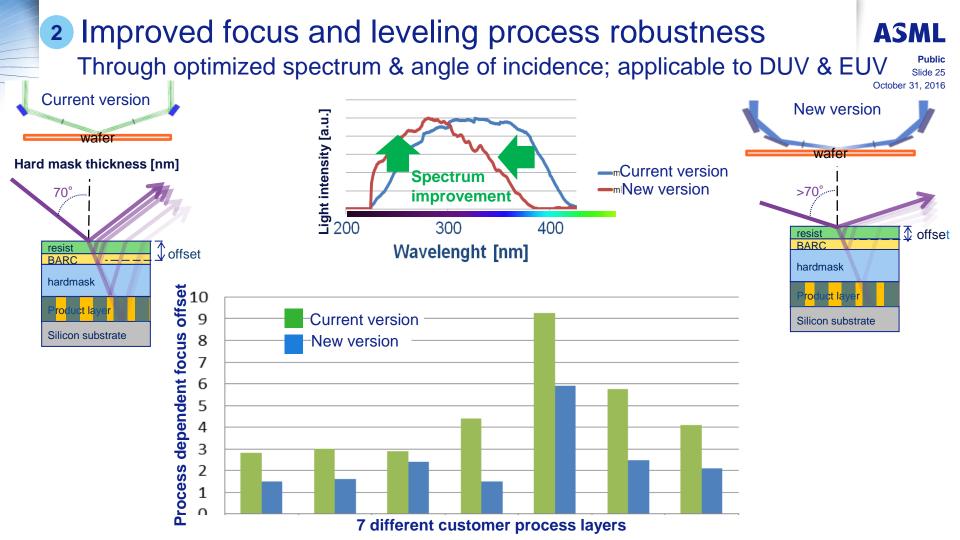

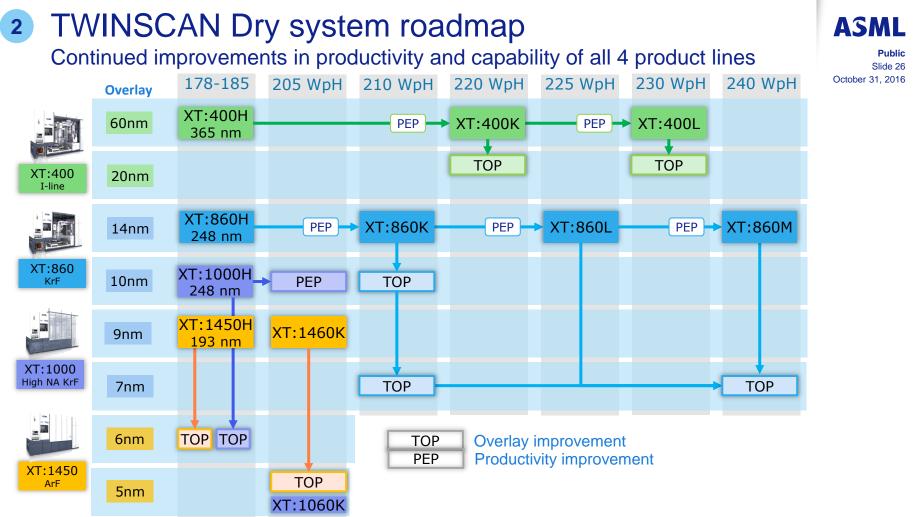

## 2 Drive DUV Competitiveness

### **ASML**

Public Slide 21 October 31, 2016

#### ...Our customers

DUV competitive • ness...

## e • Enable our customers to execute their roadmaps cost effectively

#### ...Ourselves

• Maintain our market share and margins

| DUV Strategic Pr          | DUV Strategic Priorities |           |                                               |   |  |  |

|---------------------------|--------------------------|-----------|-----------------------------------------------|---|--|--|

|                           | NXT (Immersion)          |           | XT (Dry)                                      |   |  |  |

| Technology<br>Leadership  | -                        | -         | eneration products and<br>customer priorities | k |  |  |

| Operational<br>Excellence | Deliver high qua         | lity cost | t effective solutions                         |   |  |  |

|                           |                          |           |                                               |   |  |  |

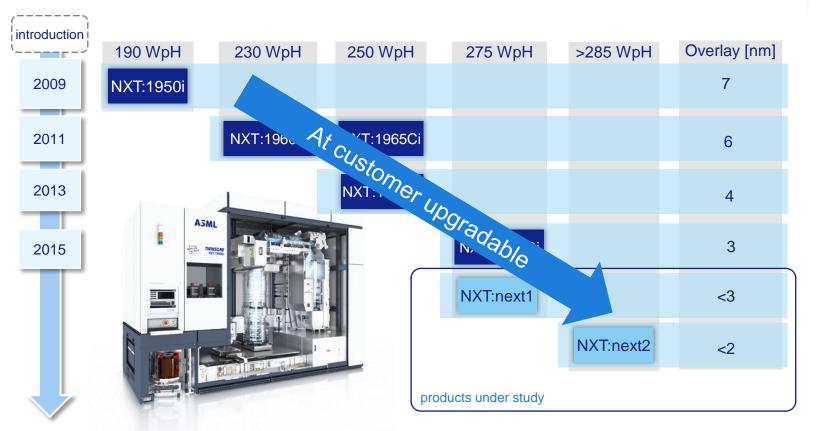

## 2 TWINSCAN Immersion system roadmap

ASML

October 31, 2016

Public Slide 22

Roadmap: October 2016

Roadmap: October 2016

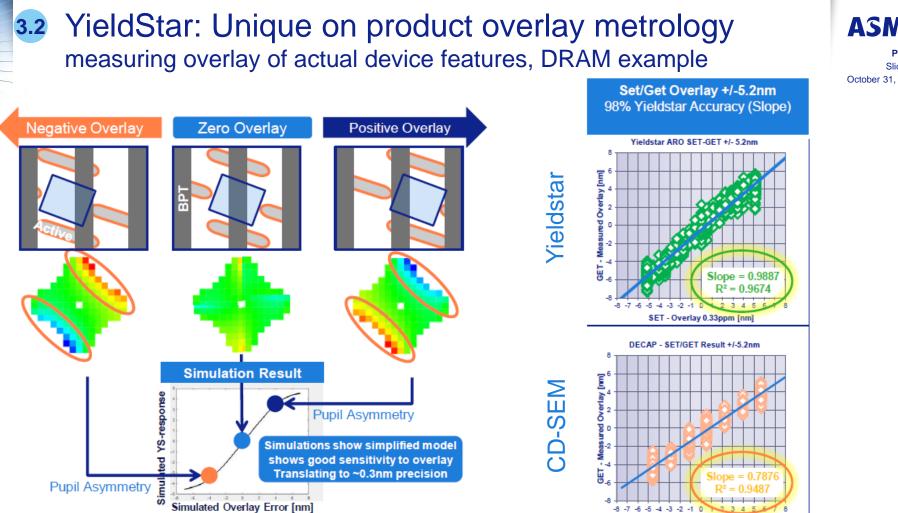

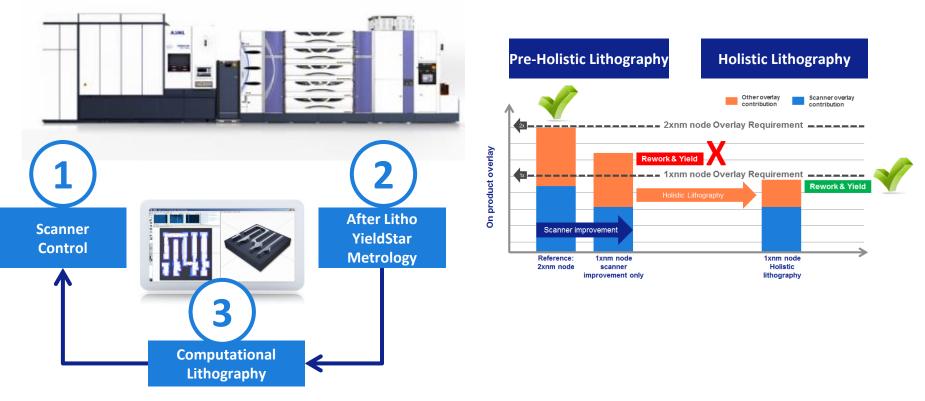

#### **ASML** 3 ASML Holistic Lithography integrates 3 competences Resulting in 3 customer value propositions October 31, 2016

Public

Slide 27

Other patterning tools

**Process Window Enhancement**

Stepper set up and layout optimization for maximum process window

Metrology process robust target and recipe creation, ebeam model calibration and computational guided detection.

(imaging, overlay and focus)

**Process Window Detection**

Stepper control through onproduct overlay, focus and pattern fidelity feedback loops.

SET - Overlay 0.33ppm [nm]

## ASML

Public Slide 28 October 31, 2016

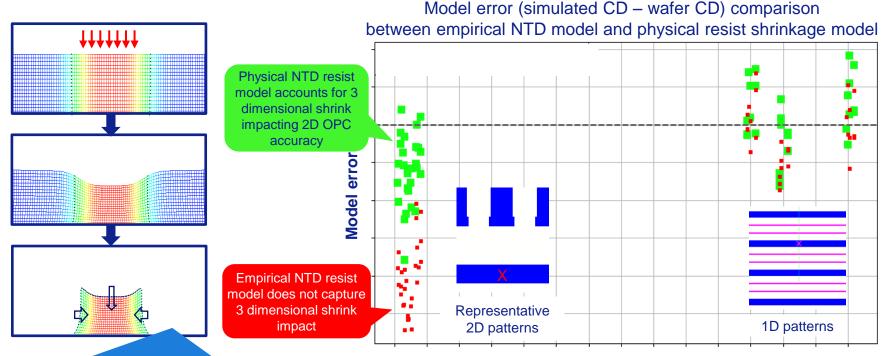

## **3.3 Unique Negative Tone resist modelling capability** Modelling accuracy improved 60%

Public Slide 29 October 31, 2016

**Customer's patterns**

NTD: the same features are printed in positive resist using light-field masks, with consequently better image contrast; with NTD the exposed resist areas remain intact. However, this approach involves additional processing steps (typically coating, baking, etching) and the exposed area is affected in 3 dimensional ways (see open arrows)

## 3 ASML holistic lithography at 1x nm node: Overlay Control ASML

Public Slide 30 October 31, 2016

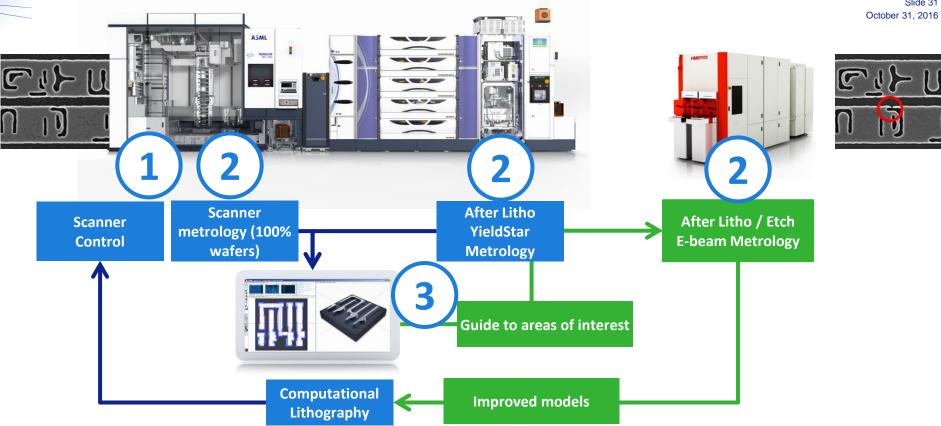

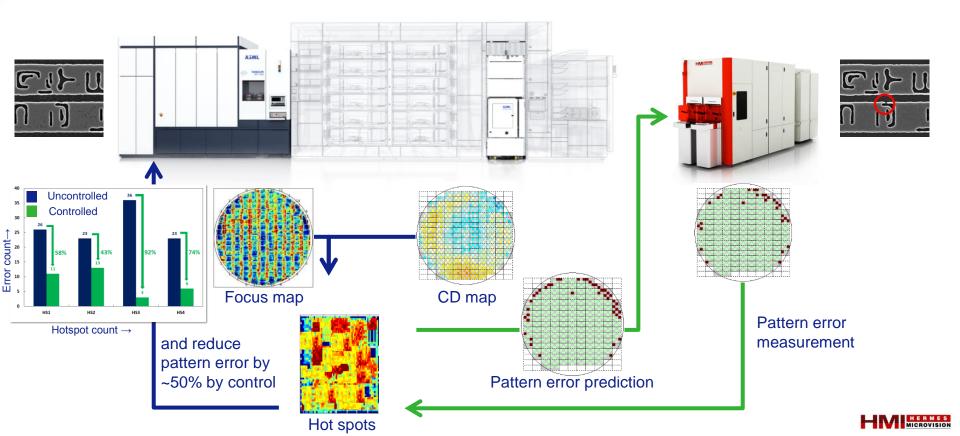

## 3 ASML holistic lithography future - Pattern fidelity control ASML

Public Slide 31 3 ASML holistic lithography future: Pattern fidelity control: reducing pattern errors up to~ 50%

Public Slide 32 October 31, 2016

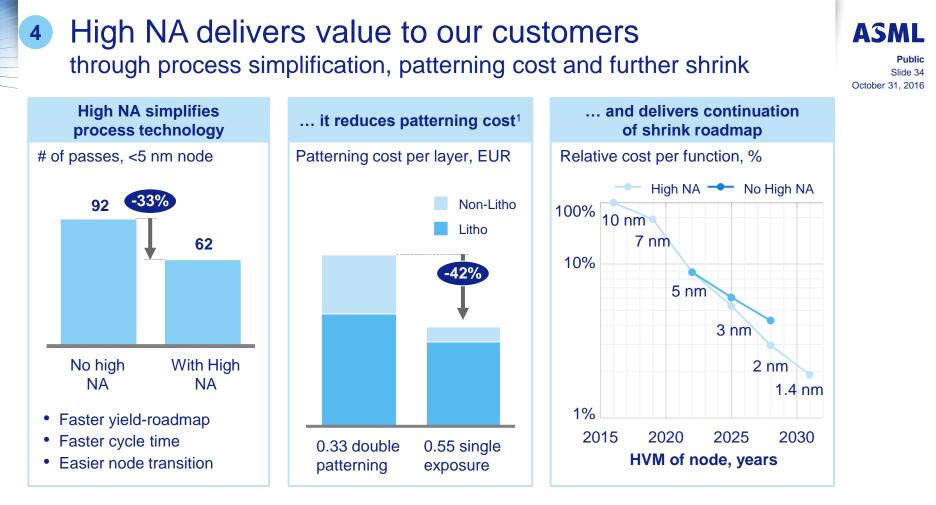

## 4 EUV with high-NA key to extending device shrink roadmaps and simplifying multiple patterning

Public Slide 33 October 31, 2016

|  | <b>DRAM</b><br>Active   | Node         | D20-22          | D1X             | D1Y                | D1Z                | next               |  |

|--|-------------------------|--------------|-----------------|-----------------|--------------------|--------------------|--------------------|--|

|  |                         | ArFi 1.35 NA | SE              | LE <sup>2</sup> | PD+LE <sup>2</sup> | PQ+LE <sup>2</sup> | PQ+LE <sup>2</sup> |  |

|  | Cut                     | EUV 0.33 NA  |                 |                 | SE                 | SE                 | LE <sup>2</sup>    |  |

|  |                         | Node         | 16-14nm         | 10nm            | 7nm                | 5nm                | 3nm                |  |

|  | Logic<br>Cuts &<br>Vias | ArFi 1.35 NA | LE <sup>2</sup> | LE <sup>3</sup> | LE <sup>3~4</sup>  | LE <sup>6~8</sup>  | LE <sup>8~11</sup> |  |

|  |                         | EUV 0.33 NA  |                 |                 | SE                 | SE                 | LE <sup>2~3</sup>  |  |

|  |                         | EUV >0.5 NA  |                 |                 |                    | SE                 | SE                 |  |

Possible but challenging

#### SE = Single Exposure, $LE^n$ = Litho-Etch, n # repeats, PD = Pitch Doubling, PQ = Pitch Quadrupling

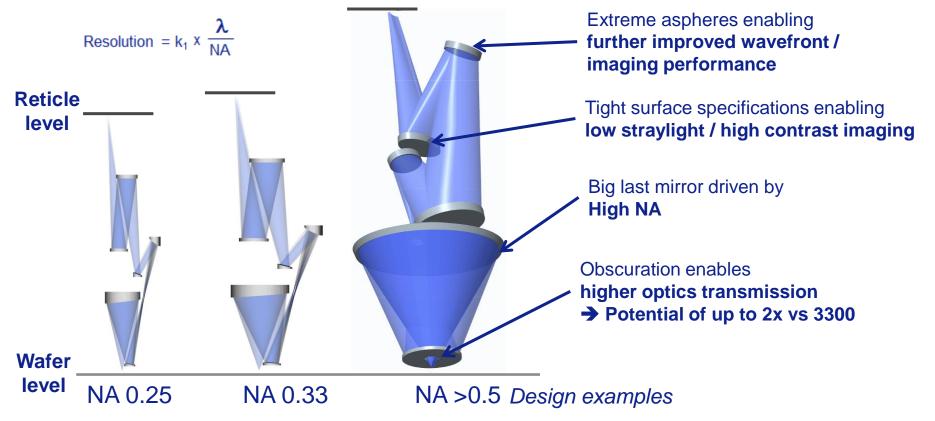

1 SE = single exposure, LE<sup>2</sup> = double patterning; Source: ASML 4 High-NA optics design concepts available Larger elements with tighter specifications

Public Slide 35 October 31, 2016

Source: Zeiss, "EUV lithography optics for sub-9nm resolution," Proc. SPIE 9422, (2015).

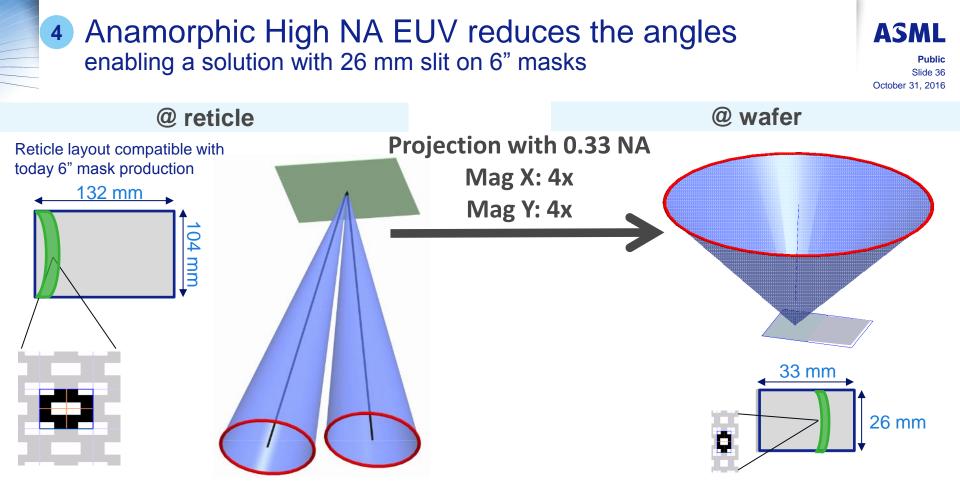

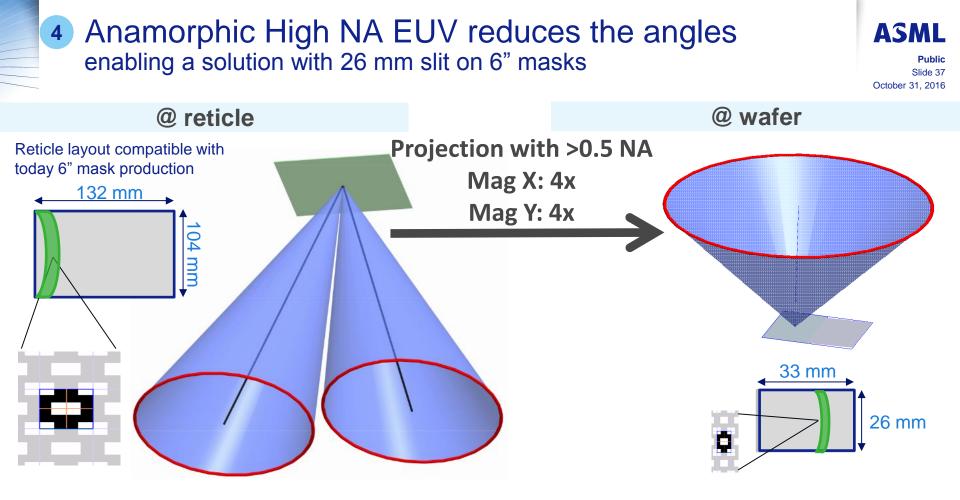

Source: Jan van Schoot, ASML, "EUV roadmap extension by higher Numerical Aperture", 2016 international symposium on EUV, 24 October 2016, Hiroshima

Source: Jan van Schoot, ASML, "EUV roadmap extension by higher Numerical Aperture", 2016 international symposium on EUV, 24 October 2016, Hiroshima

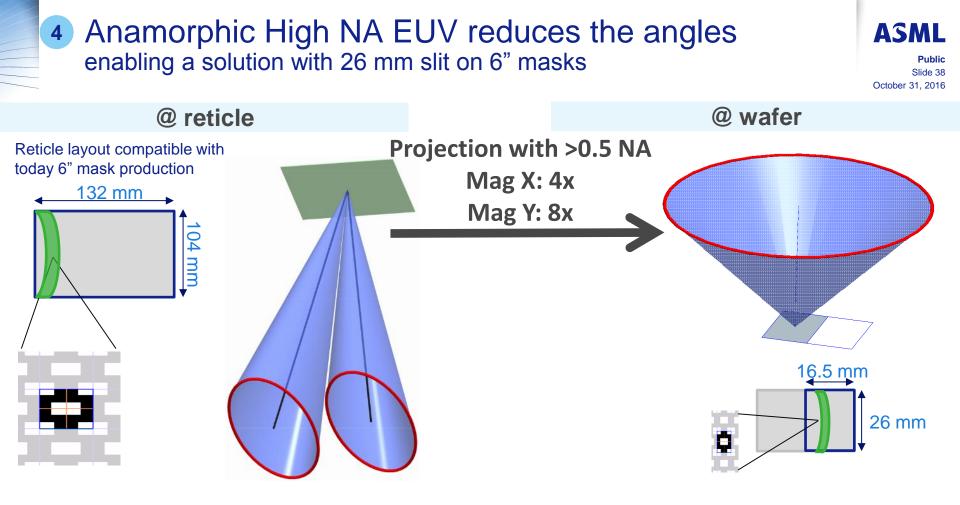

Public Slide 39 October 31, 2016

Anamorphic Lens "The Mask" (24x36mm<sup>2</sup>)

Anamorphic Projector

#### 16x9

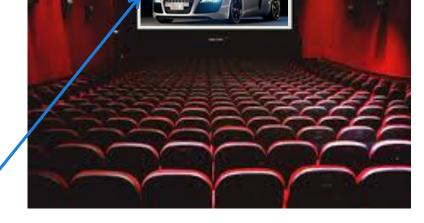

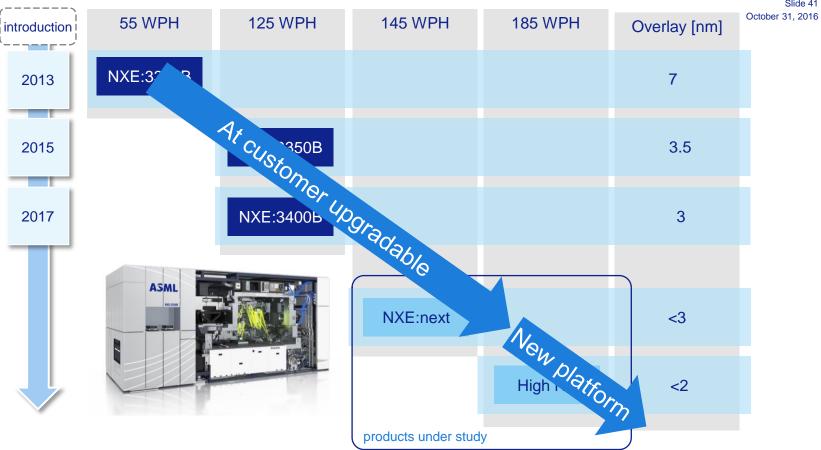

## 4 EUV extension roadmap

ASML Public Slide 41

Roadmap: October 2016

## The future

- Moore's law to continue for the foreseeable future, driven by connecting everything around us, generating massive data and enabled by geometrical device, architectural and circuit scaling. Logic device innovation and memory/computer architecture innovations in support of this.

- **EUV industrialization** enabled by identified insertion opportunity at multiple customers and execution to roadmaps progressing to plan, improvements still needed for consistency.

- **DUV competitiveness** to support continued demand given its cost advantage over EUV for less critical layers and some double patterning. Improvements in CD and overlay continued to be required for future nodes.

- Holistic Lithography is being extended with pattern fidelity control. Metrology extensions needed for on product robust process, after etch targets and resolution enhancements through computational enhanced e-beam capability. Increased scanner control capability to enable ultimate on product process control.

- EUV extension with high NA enable cost-effective shrink to continue into the next decade

Public Slide 42 October 31, 2016

## Forward looking statements

**ASML**

Public Slide 43 October 31, 2016

This document contains statements relating to certain projections and business trends that are forward-looking, including statements with respect to our outlook. including expected customer demand in specified market segments (and underlying assumptions) including memory, logic and foundry, expected sales levels, trends, including trends towards 2020 and beyond and expected industry growth, and outlook, systems backlog, expected or indicative market opportunity, financial results and targets, including, for ASML and ASML and HMI combined, expected sales, other income, gross margin, R&D and SG&A expenses, capital expenditures, cash conversion cycle. EPS and effective annualized tax rate, annual revenue opportunity and EPS potential by end of decade and growth opportunity beyond 2020 for ASML and ASML and HMI combined, cost per function reduction and ASML system ASP, goals relating to gross cash balance and ASML's capital structure, customer, partner and industry roadmaps, productivity of our tools and systems performance, including EUV system performance (such as endurance tests), expected industry trends and expected trends in the business environment, the addition of value through delivery of lithography products and the achievement of cost-effective shrink, expected continued lithography demand and increasing lithography spend, the main drivers of lithography systems, lithography intensity for all market segments, customer execution of shrink roadmaps, future memory application distribution, expected addressable markets, including the market for lithography systems and service and options, expected manufacturing and process R&D, statements with respect to growing end markets that require fab capacity driving demand for ASML's tools, statements with respect to the acquisition of HMI by ASML, including market opportunity, the expected timing of completion of the HMI acquisition and delisting of HMI. the expected benefits of the acquisition of HMI by ASML, including expected continuation of year on year growth, the provision of e-beam metrology capability and its effect on holistic lithography solutions, including the introduction of a new class of pattern fidelity control and the improvement of customers' control strategy, statements with respect to EUV, including targets, such as availability, productivity, facilities and shipments, including the number of EUV systems expected to be shipped and timing of shipments, and roadmaps, shrink being key driver to industry growth, expected industry adoption of EUV and statements with respect to plans of customers to insert EUV into production and timing, the benefits of EUV, including expected cost reduction and cost-effective shrink, the expected continuation of Moore's law, without slowing down, and that EUV will continue to enable Moore's law and drive long term value, goals for holistic lithography, including pattern fidelity control, expectations relating to double patterning, immersion and dry systems, intention to return excess cash to shareholders, statements about our proposed dividend, dividend policy and intention to repurchase shares and statements with respect to the current share repurchase plan. You can generally identify these statements by the use of words like "may", "will", "could", "should", "project", "believe", "anticipate", "expect", "plan", "estimate", "forecast", "potential", "intend", "continue" and variations of these words or comparable words. These statements are not historical facts, but rather are based on current expectations, estimates, assumptions and projections about the business and our future financial results and readers should not place undue reliance on them.

Forward-looking statements do not guarantee future performance and involve risks and uncertainties. These risks and uncertainties include, without limitation, economic conditions, product demand and semiconductor equipment industry capacity, worldwide demand and manufacturing capacity utilization for semiconductors (the principal product of our customer base), including the impact of general economic conditions on consumer confidence and demand for our customers' products, competitive products and pricing, the impact of any manufacturing efficiencies and capacity constraints, performance of our systems, the continuing success of technology advances and the related pace of new product development and customer acceptance of new products including EUV, the number and timing of EUV systems expected to be shipped and recognized in revenue, delays in EUV systems production and development, our ability to enforce patents and protect intellectual property rights, the risk of intellectual property litigation, availability of raw materials and critical manufacturing equipment, trade environment, changes in exchange rates, changes in tax rates, available cash and liquidity, our ability to refinance our indebtedness, distributable reserves for dividend payments and share repurchases and timing of resumption of the share repurchase plan, and other risks indicated in the risk factors included in ASML's Annual Report on Form 20-F and other filings with the US Securities and Exchange Commission. These forward-looking statements are made only as of the date of this document. We do not undertake to update or revise the forward-looking statements, whether as a result of new information, future events or otherwise.

## INVESTOR DAY ASMLS////TALK2016 NEW YORK CITY

The database in the state in the second seco