# Role of EUV and its Business Opportunity

Hans Meiling Vice President Product Management EUV

31 October 2016

ASMLSMALLTALK2016 NEW YORK CITY

Public Slide 2 October 31, 2016

## Agenda

- Why?

- How?

- When?

## EUV reduces multi-pattern process complexity # Process steps per layer

Public Slide 3 October 31, 2016

Why

|                                                                                                | LOGIC       | ,           |                                     |                           | DRAM                     |                           |

|------------------------------------------------------------------------------------------------|-------------|-------------|-------------------------------------|---------------------------|--------------------------|---------------------------|

| CMP<br>Dry Etch<br>Metrology<br>Lithography<br>Coat/Dev<br>Deposition<br>Wet Etch<br>Hard mask |             |             |                                     |                           |                          |                           |

|                                                                                                | ArFi<br>LE3 | ArFi<br>LE4 | ArFi spacer<br>grating<br>w/ 2 cuts | EUV<br>single<br>exposure | ArFi<br>Cross-<br>spacer | EUV<br>single<br>exposure |

LE3=Litho+Etch+Litho+Etch+Litho+Etch

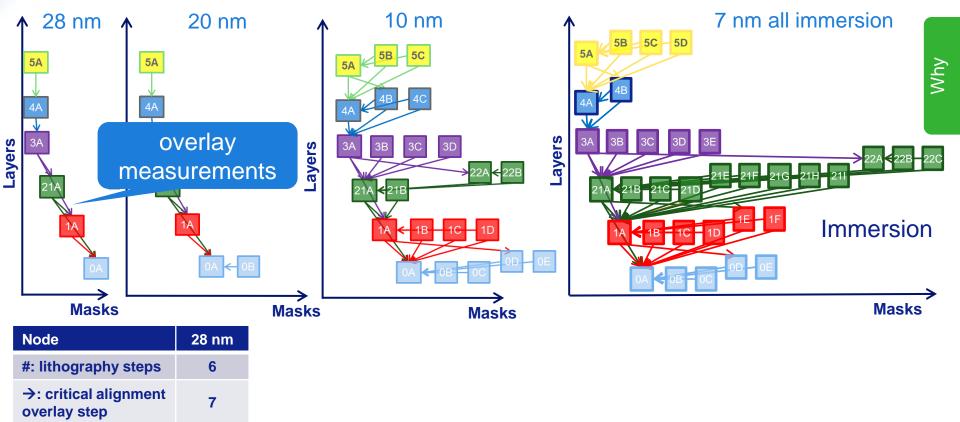

# Multi-patterning complexity explodes using immersion

Public Slide 4 October 31, 2016

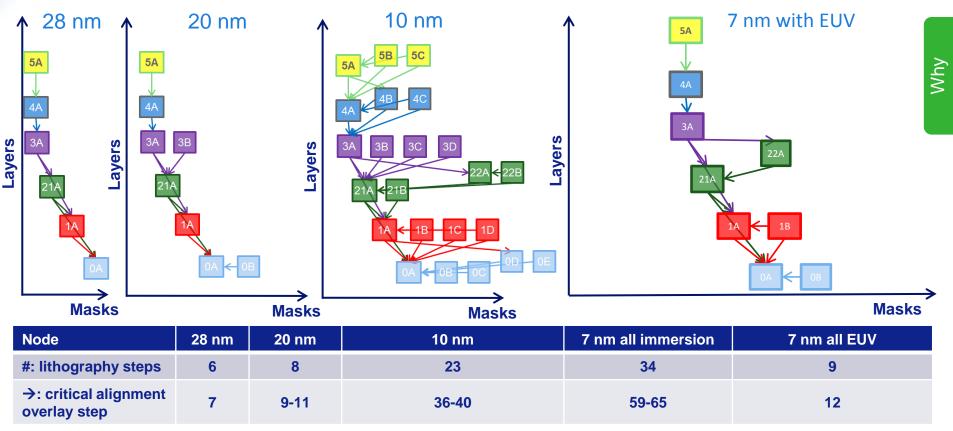

# Patterning complexity reduced with EUV through less patterning and metrology steps

Public Slide 5 October 31, 2016

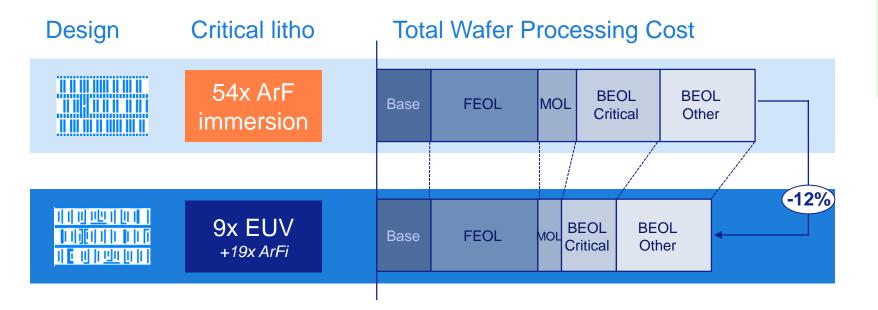

7 nm study with leading Logic chip maker projects lower wafer cost for EUV based processes

Cost per wafer calculated for ASML cost model, all process steps

ASML

Public

Slide 6 October 31, 2016

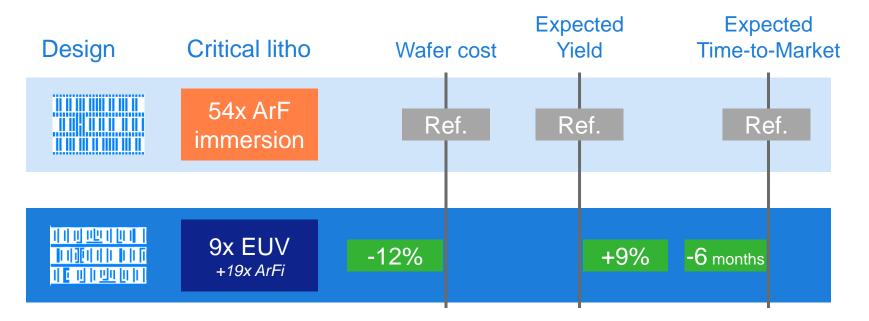

# Logic motivation – lower cost, higher yield, and faster time-to-market

Public Slide 7 October 31, 2016

Why

Public Slide 8 October 31, 2016

## Agenda

- Why?

- How?

- When?

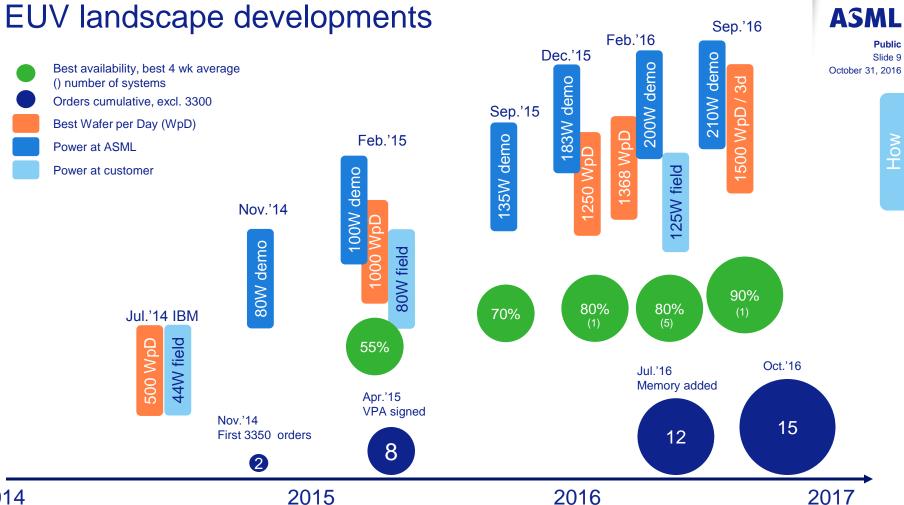

2014

Hov

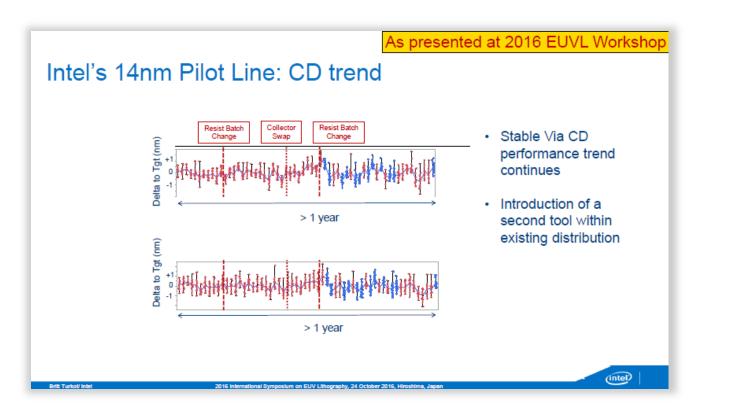

## Good EUV litho performance in 14nm Pilot line Via CD has been very stable over 1 year of operational time

Source: Britt Turkot (Intel), EUVL Symposium, Hiroshima, Japan (24-26 Oct 2016).

# Hok

## **ASML**

Public Slide 10 October 31, 2016

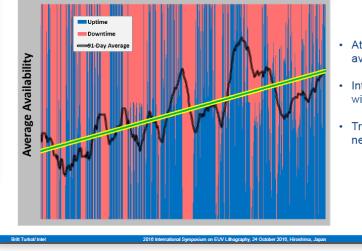

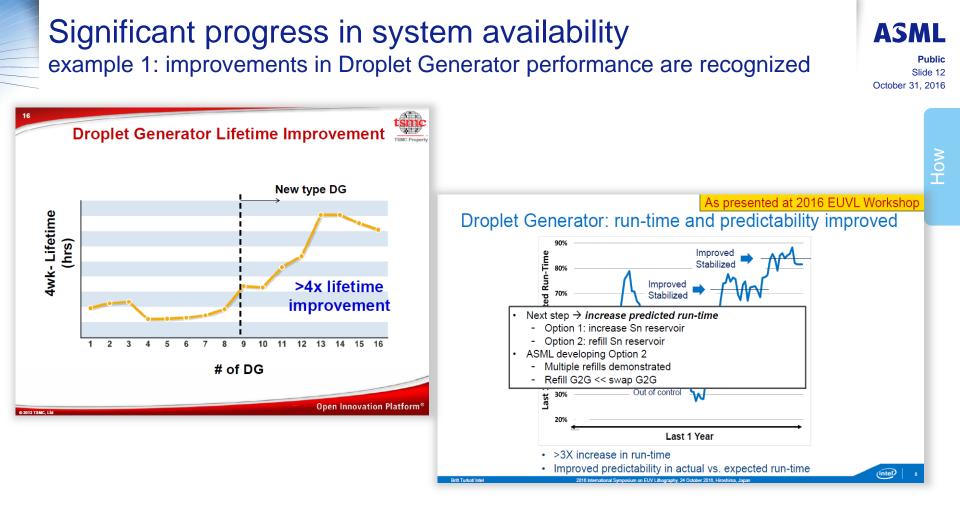

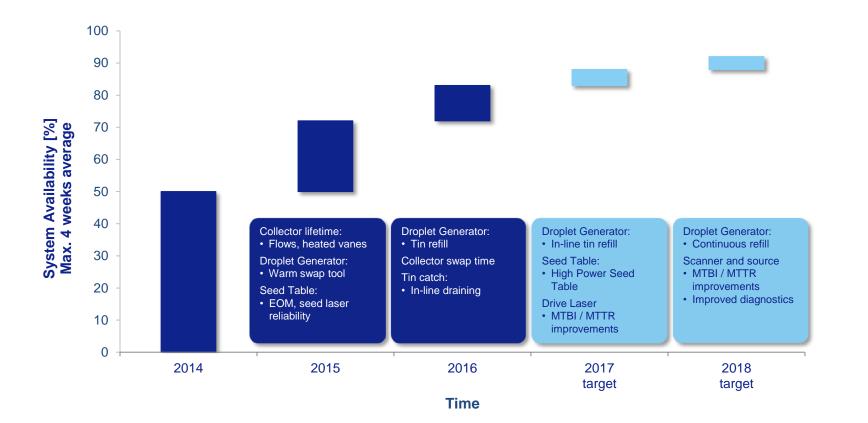

# Significant progress in system availability consistency of Availability needs further improvement

#### **EUV Scanner Availability**

Availability is improving.

#### Combined Scanner/Source Availability

ASML

Public Slide 11 October 31, 2016

Ho≷

- Introduction of NXE:3350 with no XLD so far

- Trend in right direction, but needs to be faster

(intel)

Source: Intel and TSMC presentations at EUVL Symposium, Hiroshima, Japan (24-26 Oct 2016).

Source: Intel and TSMC presentations at EUVL Symposium, Hiroshima, Japan (24-26 Oct 2016).

## Roadmap in place towards >90% availability Significant progress since 2014, consistency must be improved

Public Slide 13 October 31, 2016

> H0 ≷

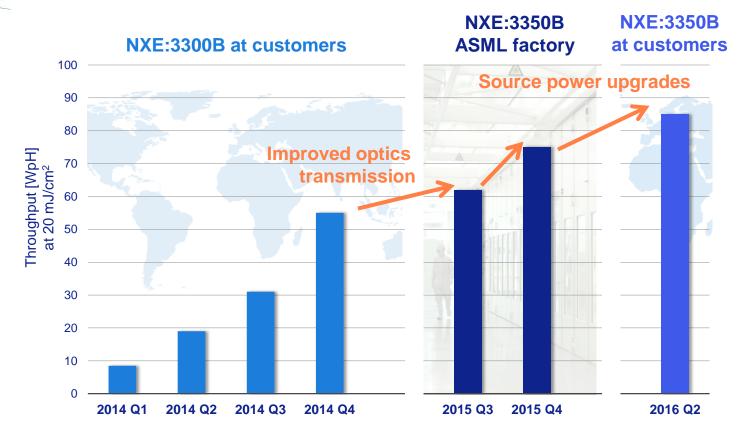

## Productivity continues to improve 85 WpH (wafers per hour) achieved with 125W configuration

Slide 14 October 31, 2016

Public

NXE:3350B ATP test: 26x33mm2, 96 fields, 20mJ/cm<sup>2</sup>

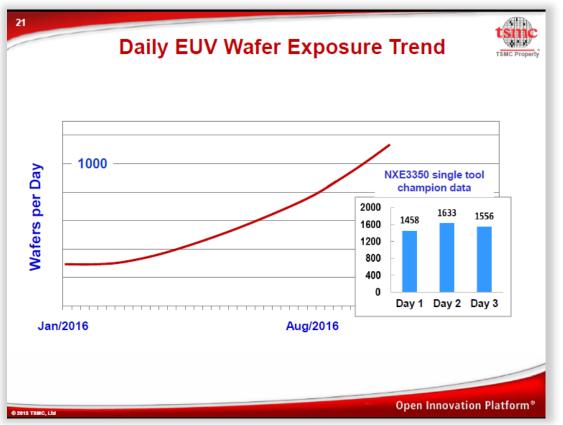

Productivity improvement also available to customers 3-day average of >1500 WpD achieved on NXE:3350B

Source: L.J. Chen (TSMC), EUVL Symposium, Hiroshima, Japan (24-26 Oct 2016).

ASML

Public Slide 15 October 31, 2016

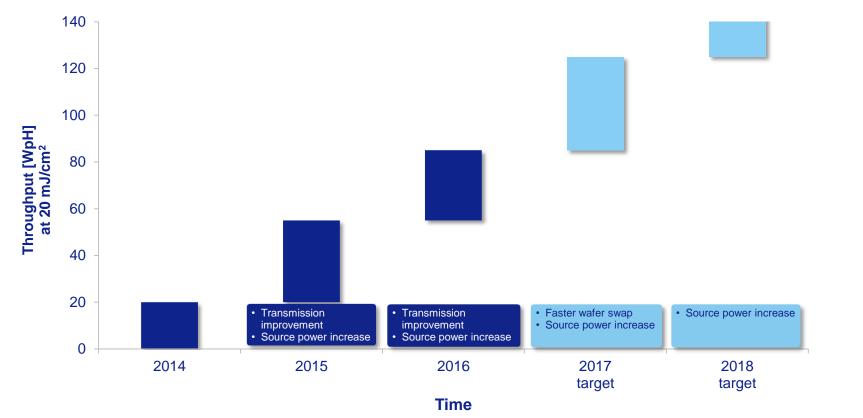

# Throughput roadmap towards >125 WpH in place

ASML

Public Slide 16 October 31, 2016

Hov

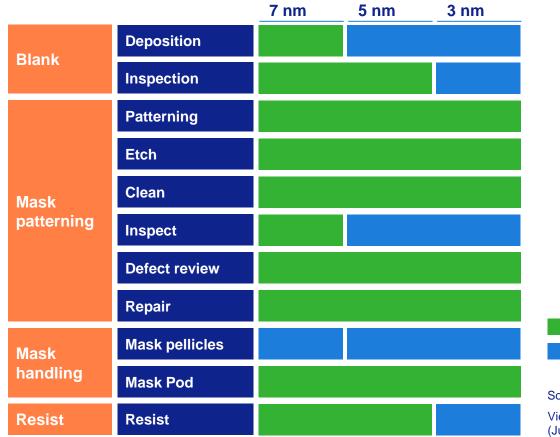

# EUV infrastructure is viable for 7 nm node improvements required for 5 nm

## **ASML**

Public Slide 17 October 31, 2016

Secured

Improvements required

Source: ASML Research, VLSI

View confirmed by recent Intel reports (June & September 2016)

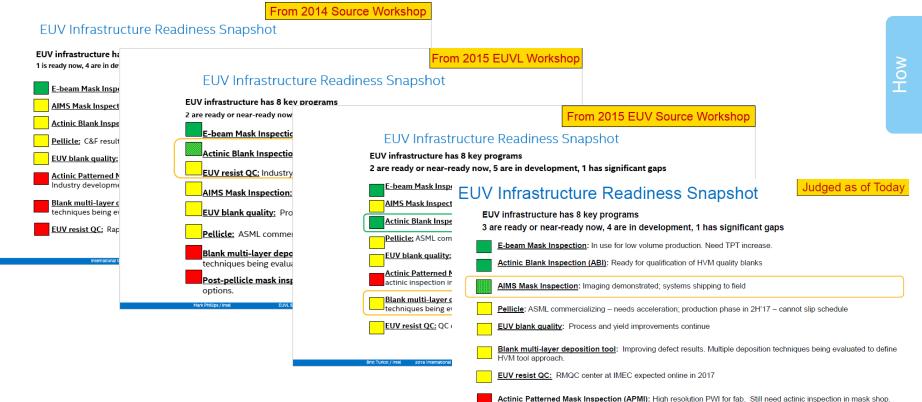

# **Evolution of Infrastructure readiness**

## ASML

Public Slide 18 October 31, 2016

Source: Britt Turkot (Intel), EUVL Symposium, Hiroshima, Japan (24-26 Oct 2016).

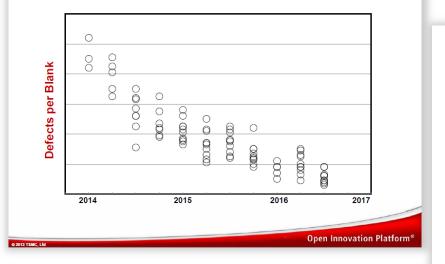

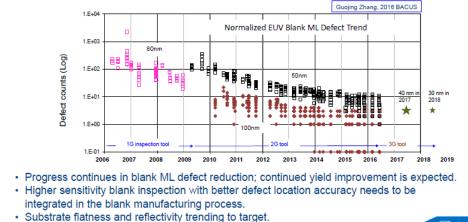

# Continued improvement in mask defects will lead to yield improvements

Continual reduction of mask native defects

# EUV blank guality and defectivity improving

Source: Intel and TSMC presentations at EUVL Symposium, Hiroshima, Japan (24-26 Oct 2016).

October 31, 2016

(intel)

# NXE Pellicles are being mounted and used in scanners

October 31, 2016

NOK

# 124

## Durability measured to >85 WpH

## Pellicle on integration mounting tooling

# Progress resist materials: towards 16 nm resolution at 125 WpH

## **ASML**

Public Slide 21 October 31, 2016

|                                        | 16 nm Horizontal<br>Dense lines/spaces |                        |                                    | 13 nm Horizontal<br>Dense lines/spaces |                       |     |

|----------------------------------------|----------------------------------------|------------------------|------------------------------------|----------------------------------------|-----------------------|-----|

|                                        | NXE:3350<br>Reference CAR              | New formulation<br>CAR | New Inpria resist<br>(NTI non-CAR) | CAR                                    | Non-CAR               |     |

| SEM image<br>@BE/BF<br>(90deg rotated) |                                        |                        |                                    |                                        |                       |     |

| Dose                                   | 40 mJ/cm <sup>2</sup>                  | 25 mJ/cm <sup>2</sup>  | 18.5 mJ/cm <sup>2</sup>            | ~40 mJ/cm <sup>2</sup>                 | 31 mJ/cm <sup>2</sup> |     |

| Prod                                   | uctivity improveme                     | ent                    |                                    |                                        |                       |     |

| LWR                                    | 4.6 nm                                 | 5.2 nm                 | 4.4 nm                             | 4.5 nm                                 | 4.2 nm                |     |

| Imag                                   | ing improvement                        |                        |                                    |                                        |                       |     |

|                                        |                                        |                        | Înpria                             |                                        | Ânr                   | ori |

Exposures done on NXE:3350B system with Dipole Y illumination. LWR: Line Width Roughness

Public Slide 22 October 31, 2016

## Agenda

- Why?

- How?

- When?

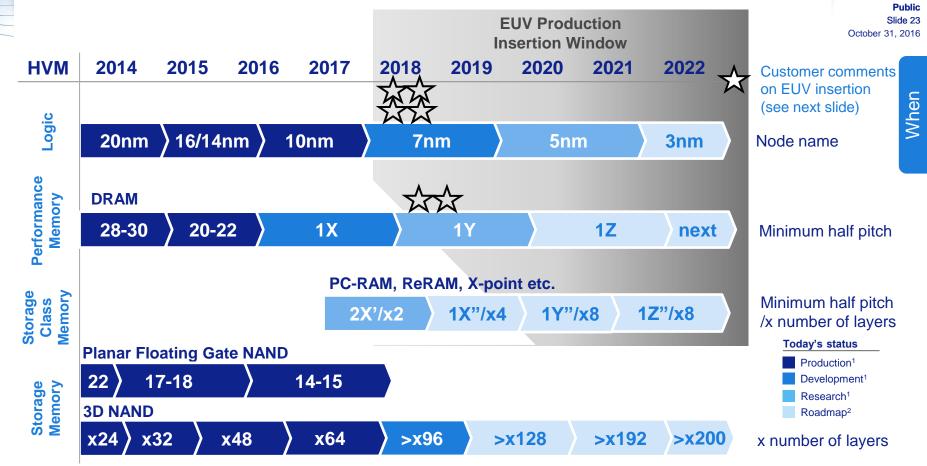

# Industry Shrink Roadmap & EUV insertion

Source: 1) Customers - public statements,, IC Knowledge LLC; 2) ASML extrapolations

## Customers plan to insert EUV into production in 2018/19

### **Customer public statements on EUV HVM insertion**

ASML

Public

When

Slide 24 October 31, 2016

Source: L.J. Chen (TSMC), EUVL Symposium, Hiroshima, Japan (24-26 Oct 2016).

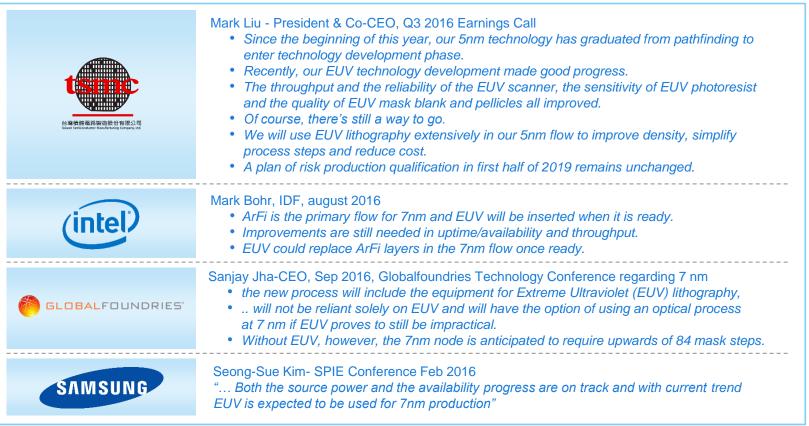

## Customers plan to insert EUV into production in 2018/19

ASML

Slide 25 October 31, 2016

When

## Customer public statements on EUV HVM insertion

#### Source: Customer public statements

# Customers plan to insert EUV into production in 2018/19

### **Customer public statements on EUV HVM insertion**

Kim Jun-Ho, Q2 2016 Earnings call:

"...we also are planning to start the development for the 1Y nano and for this, EUV that has been used for R&D, ... whether EUV will be adopted in full for 1Y nano, we cannot say at this point. But one thing is for sure and that is we will use EUV for mass production of 1Z nano and that is going to be in 2019."

Seong-Sue Kim- SPIE Conference Feb 2016 ... Feasibility proved for both L7 and D1Y patterning " ASML

Public Slide 26 October 31, 2016

Source: Customer public statements

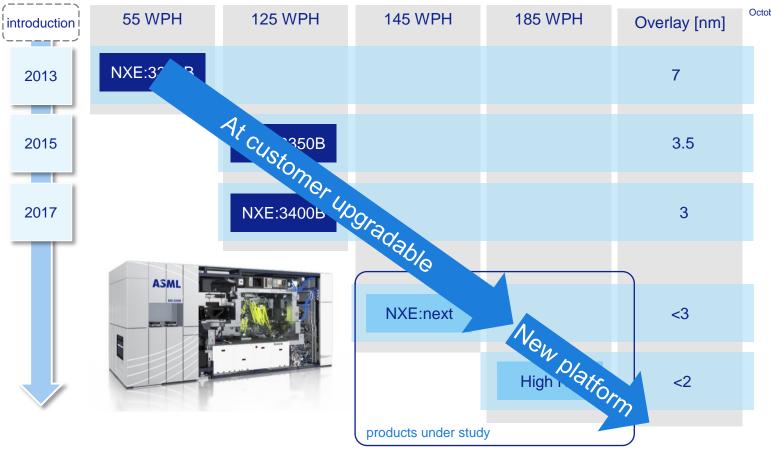

# EUV extension roadmap

ASML

Public

Slide 27 October 31, 2016

Roadmap: October 2016

## EUV estimated demand per fab by market Range of layers and corresponding systems per fab\*

| Market                                 | Fab Capacity<br>(kwspm) | EUV layers | EUV<br>systems/fab | ArFi<br>systems/fab |

|----------------------------------------|-------------------------|------------|--------------------|---------------------|

| Logic                                  | 45                      | 6 - 10     | 7 - 12             | 21 - 16             |

| Performance<br>Memory                  | 100                     | 1 - 2      | 2 - 4              | 16 - 14             |

| Storage<br>Class Memory<br>(ie. ReRAM) | 80                      | 0 or 9     | 0 or 13            | 18 or 6             |

kwspm: x1000 wafer starts per month

\*"Typical" process and system conditions in the 2018-2020 timeframe, not specific customer condition

ASML

Public Slide 28 October 31, 2016

# EUV facilities and supply chain supports demand

## ASML

Public Slide 29 October 31, 2016

**2014:** EUV: 15 cabins

**2015:** new EUV cleanroom: +10 cabins 201x: EUV: +10 cabins when needed, shell ready

# ZEISS

EUV factory cleanrooms in place

New cleanroom announced in June 2015

TRUMPF

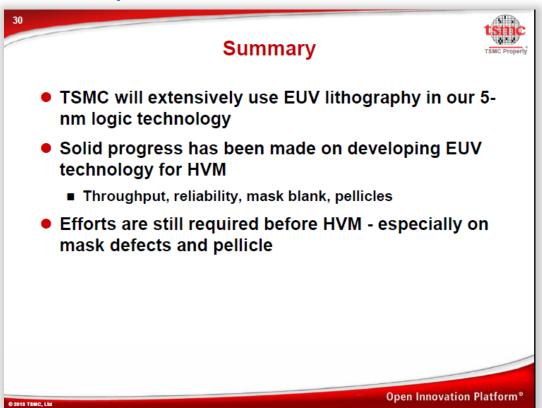

# **EUV** summary

#### Availability

- Best performance is four-week average above 90% on a NXE:3300B system

- Seven customer systems have achieved a four-week average availability >80%, consistency between tools and across sites still needs to be significantly improved

- Roadmap to >90% availability, with consistent performance, in place

#### Productivity

More than 1,500 wafers per day (WpD) exposed on a NXE:3350B at a customer site on average over three days at 85WpH configuration. Roadmap in place to secure >125WpH

#### Infrastructure

• EUV infrastructure is developing in sync with 7nm node insertion timing; further improvements required for 5nm node

Insertion

• ASML expects that customers will take EUV into production in 2018-2019 timeframe

## ASML

Public Slide 30 October 31, 2016

# Forward looking statements

Slide 31 October 31, 2016

This document contains statements relating to certain projections and business trends that are forward-looking, including statements with respect to our outlook. including expected customer demand in specified market segments (and underlying assumptions) including memory, logic and foundry, expected sales levels, trends, including trends towards 2020 and beyond and expected industry growth, and outlook, systems backlog, expected or indicative market opportunity, financial results and targets, including, for ASML and ASML and HMI combined, expected sales, other income, gross margin, R&D and SG&A expenses, capital expenditures, cash conversion cycle, EPS and effective annualized tax rate, annual revenue opportunity and EPS potential by end of decade and growth opportunity beyond 2020 for ASML and ASML and HMI combined, cost per function reduction and ASML system ASP, goals relating to gross cash balance and ASML's capital structure, customer, partner and industry roadmaps, productivity of our tools and systems performance, including EUV system performance (such as endurance tests), expected industry trends and expected trends in the business environment, the addition of value through delivery of lithography products and the achievement of cost-effective shrink. expected continued lithography demand and increasing lithography spend, the main drivers of lithography systems, lithography intensity for all market segments, customer execution of shrink roadmaps, future memory application distribution, expected addressable markets, including the market for lithography systems and service and options, expected manufacturing and process R&D, statements with respect to growing end markets that require fab capacity driving demand for ASML's tools, statements with respect to the acquisition of HMI by ASML, including market opportunity, the expected timing of completion of the HMI acquisition and delisting of HMI, the expected benefits of the acquisition of HMI by ASML, including expected continuation of year on year growth, the provision of e-beam metrology capability and its effect on holistic lithography solutions, including the introduction of a new class of pattern fidelity control and the improvement of customers' control strategy, statements with respect to EUV, including targets, such as availability, productivity, facilities and shipments, including the number of EUV systems expected to be shipped and timing of shipments, and roadmaps, shrink being key driver to industry growth, expected industry adoption of EUV and statements with respect to plans of customers to insert EUV into production and timing, the benefits of EUV, including expected cost reduction and cost-effective shrink, the expected continuation of Moore's law, without slowing down, and that EUV will continue to enable Moore's law and drive long term value, goals for holistic lithography, including pattern fidelity control, expectations relating to double patterning, immersion and dry systems, intention to return excess cash to shareholders, statements about our proposed dividend, dividend policy and intention to repurchase shares and statements with respect to the current share repurchase plan. You can generally identify these statements by the use of words like "may", "will", "could", "should", "project", "believe", "anticipate", "expect", "plan", "estimate", "forecast", "potential", "intend", "continue" and variations of these words or comparable words. These statements are not historical facts, but rather are based on current expectations, estimates, assumptions and projections about the business and our future financial results and readers should not place undue reliance on them.

Forward-looking statements do not guarantee future performance and involve risks and uncertainties. These risks and uncertainties include, without limitation, economic conditions, product demand and semiconductor equipment industry capacity, worldwide demand and manufacturing capacity utilization for semiconductors (the principal product of our customer base), including the impact of general economic conditions on consumer confidence and demand for our customers' products, competitive products and pricing, the impact of any manufacturing efficiencies and capacity constraints, performance of our systems, the continuing success of technology advances and the related pace of new product development and customer acceptance of new products including EUV, the number and timing of EUV systems expected to be shipped and recognized in revenue, delays in EUV systems production and development, our ability to enforce patents and protect intellectual property rights, the risk of intellectual property litigation, availability of raw materials and critical manufacturing equipment, trade environment, changes in exchange rates, changes in tax rates, available cash and liquidity, our ability to refinance our indebtedness, distributable reserves for dividend payments and share repurchases and timing of resumption of the share repurchase plan, and other risks indicated in the risk factors included in ASML's Annual Report on Form 20-F and other filings with the US Securities and Exchange Commission. These forward-looking statements are made only as of the date of this document. We do not undertake to update or revise the forward-looking statements, whether as a result of new information, future events or otherwise.

# INVESTOR DAY ASMLS////TALK2016 NEW YORK CITY

The database in the state in the second seco